# **SOC - Spot the Odd Circuit**

### Applications

Home, Contacts, Phone, Browser, ...

### **Application Framework**

Managers for Activity, Window, Package, ...

### Libraries

### Runtime

SQLite, OpenGL, SSL, ...

Dalvik VM, Core libs

### Linux Kernel

Display, camera, flash, wifi, audio, IPC (binder), ...

Android Software Stack

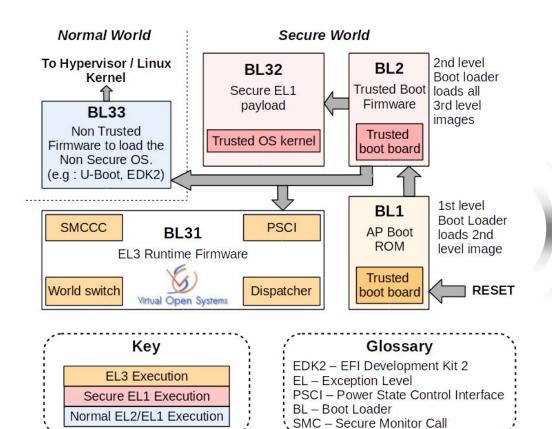

### Why SCA on a SoC might be Hard

Reality we are facing

- High Speed more than one Giga Hertz

- > Acquisition chain and setup matters

- Identify Crypto activity not that simple

- Nanometer Technology

- Two Cache Levels Cache Activities perturbates the acquisition

- Running in a complex OS context

- > Interruption

- Multiple Crypto options (SW librairies, HW)

- Several Application Options

- Acces not always easy

- HW AES Enc in 20 cycles ...

For all these reasons, studying one of the most deployed core like the ARMv8 is interesting

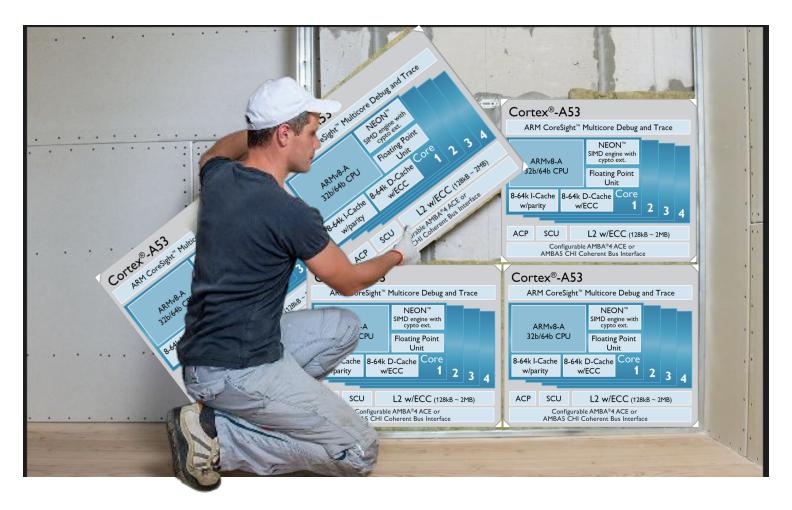

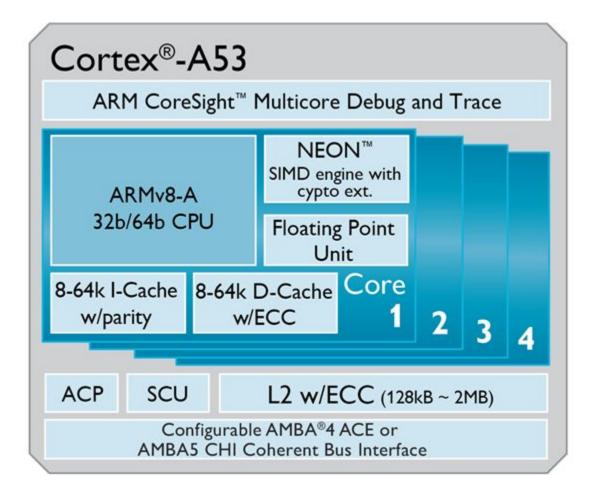

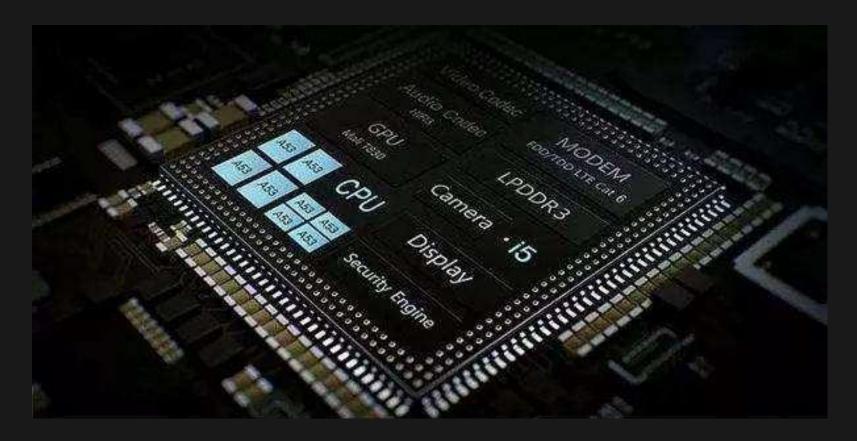

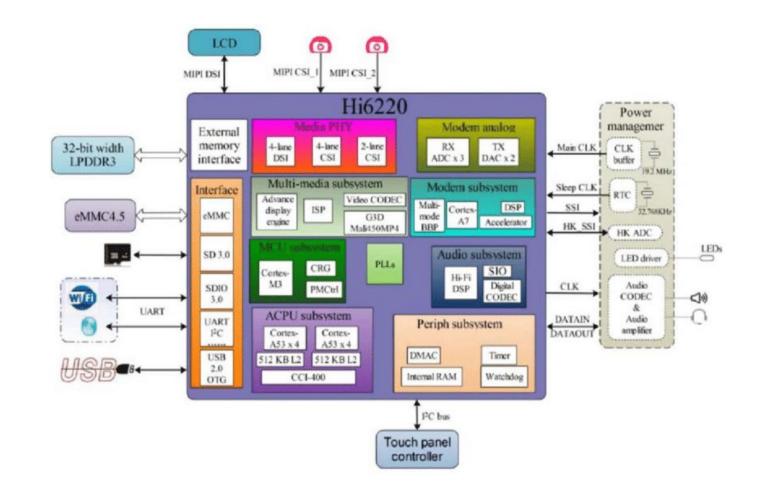

### First Target for SCA - Hisilicon Kirin 620 SoC on the Hikey board

$8 \, x \, \text{ARM} @$  A53 Cores with NEON  $^{\text{TM}}$  , Freq 1.2Ghz

😽 eShard

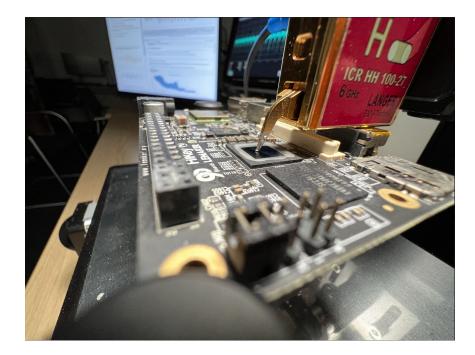

### On the SCA Bench ...

$\langle q \rangle$

### **EM Activity**

While AES encryption, using OpenSSL library

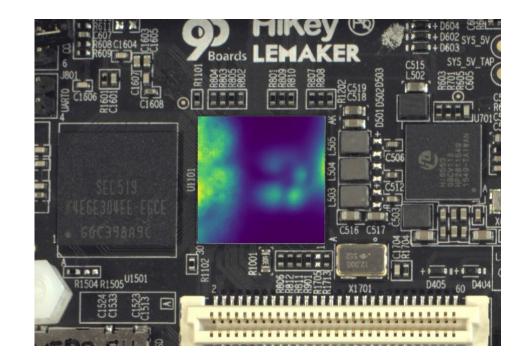

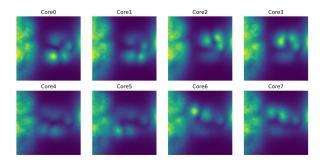

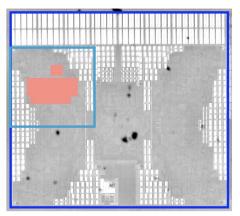

### EM Cartography - One active among the eight cores

Figure 3.3: Cartography with AES running on each Core. (top) Cluster 0-3 (bottom) Cluster 4-7

→ Core activity is visible on the right, but the PMIC (Power Management Integrated Circuit), on the left side is a source of emission

- → This a small signal processing allow to identify the activity of the active core.

- → We noticed 2 clusters 0-3 and 4-7 that seems to operate simultaneously

- $\rightarrow$  Core 0, 3, and 6 have a stronger emission

Figure 3.4: Localization of each core by signal amplitude difference

### Some results in OpenSSL context

- Mode of operations

- Interruptions

- Cache L1/L2

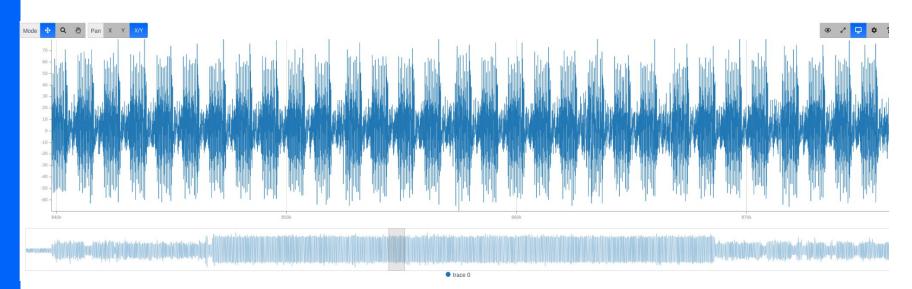

## Mode of Operation Matters

### Mode of Operation

ECB

$\langle \boldsymbol{q} \rangle$

### Mode of Operation

CBC

trace 0

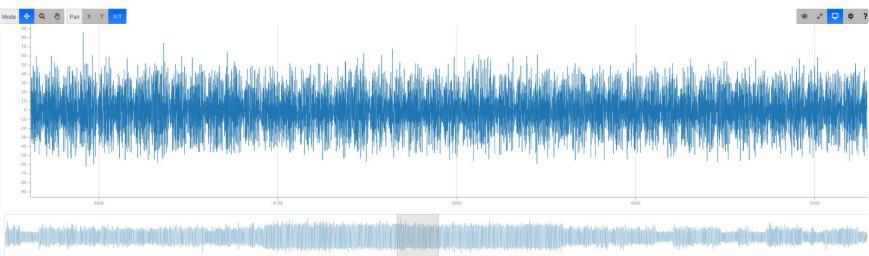

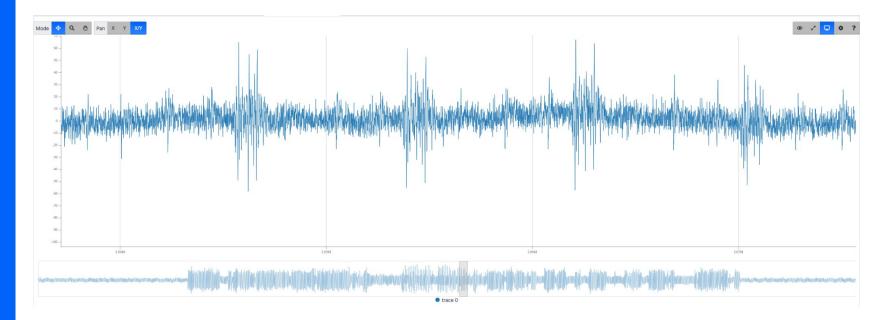

### At OS Level...

$\langle q \rangle$

### Interruptions, every 4ms

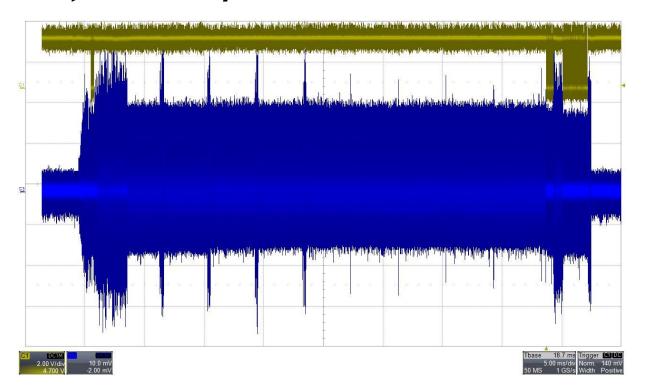

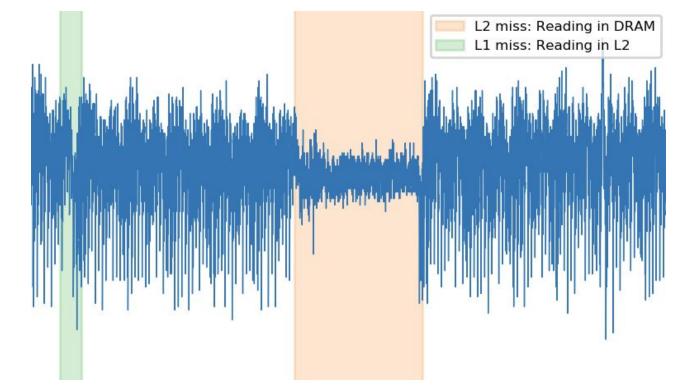

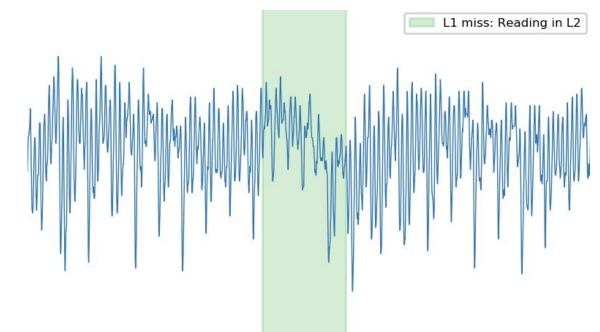

## **Memory Operations - Cache Effects**

### **Cache Miss**

### L1 Miss Read in L2

## But, ... cache activity (here L1) can be identified

### Attack Strategy - Divide and Conquer (always ...)

Let's simplify the work, then scale-up ... may the Force be with us!

### **Classical Approach**

Simplify but not too much

- Known Inputs or Output of targeted Algorithm

- Known Code

- Control the Core(s) where the AES is operated

- Add triggers to ease identification

| 1  | func decrypt   |                   |                                                    |

|----|----------------|-------------------|----------------------------------------------------|

| 2  | ldr            | x3, =0xf9818010   |                                                    |

| 3  | ld1            | { v0.16B }, [x3]  | <pre>// Loading from memory to NEON register</pre> |

| 4  |                |                   |                                                    |

| 5  | aesd           | v0.16B, v11.16B   | // First Round decrypt                             |

| 6  | aesimc         | v0.16B, v0.16B    | // Inverse MixColumns                              |

| 7  | aesd           | v0.16B, v10.16B   |                                                    |

| 8  | aesimc         | v0.16B, v0.16B    |                                                    |

| 9  | aesd           | v0.16B, v9.16B    |                                                    |

| 10 | aesimc         | v0.16B, v0.16B    |                                                    |

| 11 | aesd           | v0.16B, v8.16B    |                                                    |

| 12 | aesimc         | v0.16B, v0.16B    |                                                    |

| 13 | aesd           | v0.16B, v7.16B    |                                                    |

| 14 | aesimc         | v0.16B, v0.16B    | Simple AES bare-meta                               |

| 15 | aesd           | v0.16B, v6.16B    |                                                    |

| 16 | aesimc         | v0.16B, v0.16B    |                                                    |

| 17 | aesd           | v0.16B, v5.16B    |                                                    |

| 18 | aesimc         | v0.16B, v0.16B    |                                                    |

| 19 | aesd           | v0.16B, v4.16B    |                                                    |

| 20 | aesimc         | v0.16B, v0.16B    |                                                    |

| 21 | aesd           | v0.16B, v3.16B    |                                                    |

| 22 | aesimc         | v0.16B, v0.16B    |                                                    |

| 23 | aesd           | v0.16B, v2.16B    |                                                    |

| 24 | eor            | v0.16B, v0.16B, v | 1.16B // Last AddRoundKey                          |

| 25 |                |                   |                                                    |

| 26 | st1            | { v0.16B }, [x3]  | <pre>// Storing result in-place</pre>              |

| 27 | ret            |                   |                                                    |

| 28 | endfunc decryp | t                 |                                                    |

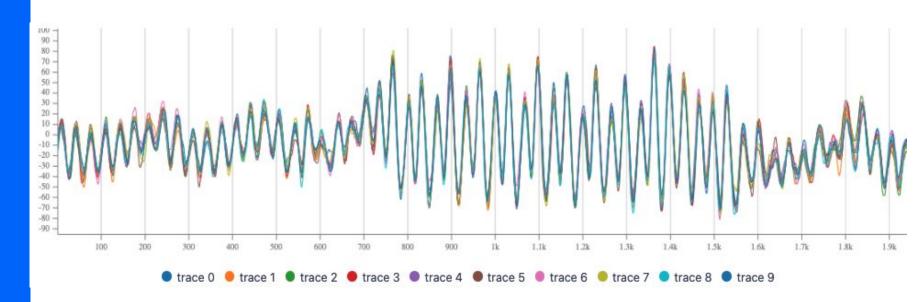

## A Single AES 10 traces synchronized

Looks good!

28

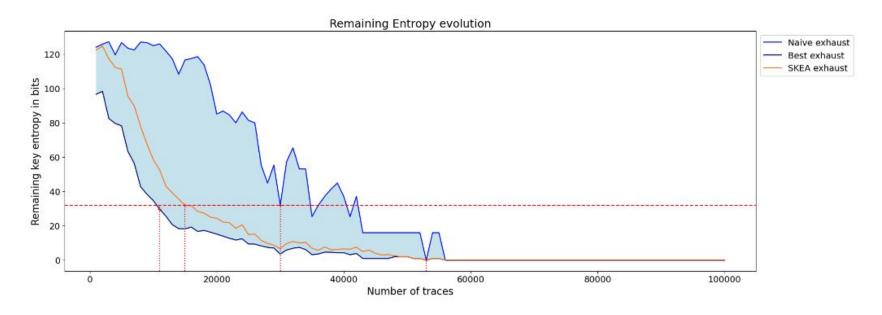

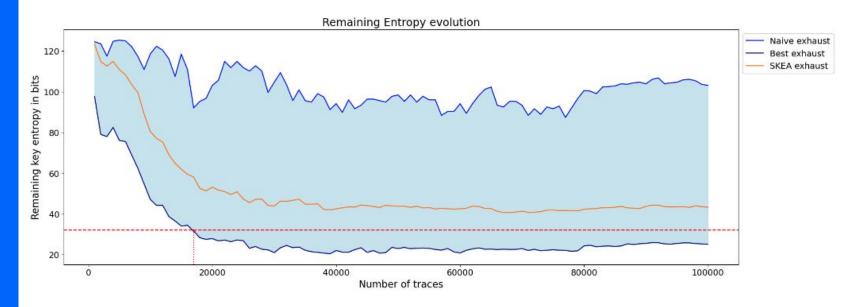

#### Remaining Key Entropy evolution - Single Core

## Pipeline Effect ?

| $1  \lor  { m fur}$ | c_decrypt_pipelined                                                                         |

|---------------------|---------------------------------------------------------------------------------------------|

|                     | ldr x3, =0xf9818010 // Pointer to input data                                                |

|                     | <pre>ld1 { v12.16B }, [x3], #16 // Loading from memory to NEON register</pre>               |

|                     | ld1 { v13.16B }, [x3], #16 // 3 blocks at a time                                            |

|                     | ld1 { v14.16B }, [x3], #16                                                                  |

|                     |                                                                                             |

|                     | aesd v12.16B, v11.16B // Round 0                                                            |

|                     | aesimc v12.16B, v12.16B                                                                     |

|                     | aesd v13.16B, v11.16B                                                                       |

| 10                  | aesimc v13.16B, v13.16B                                                                     |

| 11                  | aesd v14.16B, v11.16B                                                                       |

| 12                  | aesimc v14.16B, v14.16B                                                                     |

| 13                  |                                                                                             |

| 14                  | aesd v12.16B, v10.16B // Round 1                                                            |

| 15                  | aesimc v12.16B, v12.16B                                                                     |

| 16                  | aesd v13.16B, v10.16B                                                                       |

| 17                  | aesimc v13.16B, v13.16B                                                                     |

| 18                  | aesd v14.16B, v10.16B                                                                       |

| 19                  | aesimc v14.16B, v14.16B                                                                     |

| 20                  |                                                                                             |

| 21                  | Dipoline 2 AES here met                                                                     |

| 22                  | Pipeline 3 AES bare-met                                                                     |

| 23                  | aesd v12.16B, v3.16B                                                                        |

| 24                  | aesimc v12.16B, v12.16B                                                                     |

| 25                  | aesd v13.16B, v3.16B                                                                        |

| 26                  | aesimc v13.16B, v13.16B                                                                     |

| 27                  | aesd v14.16B, v3.16B                                                                        |

| 28                  | aesimc v14.16B, v14.16B                                                                     |

| 29                  | and with 100 wh 100 with broad                                                              |

| 30                  | aesd v12.16B, v2.16B // Last Round                                                          |

| 31                  | aesd v13.16B, v2.16B                                                                        |

| 32                  | aesd v14.16B, v2.16B                                                                        |

| 33                  | eor v12.16B, v12.16B, v1.16B                                                                |

| 34                  | eor v13.16B, v13.16B, v1.16B                                                                |

| 35                  | eor v14.16B, v14.16B, v1.16B                                                                |

| 36                  | ldr x3, =0xf9818010 // Reload pointer                                                       |

| 37                  |                                                                                             |

| 38<br>39            | <pre>st1 { v12.16B }, [x3], #16 // Storing result in-place st1 { v13.16B }, [x3], #16</pre> |

|                     | st1 { v13.106 }, [x3], #16<br>st1 { v14.168 }, [x3], #16                                    |

| 40                  | Sti (V14.10D / [X5], #10                                                                    |

| 40<br>41            | ret                                                                                         |

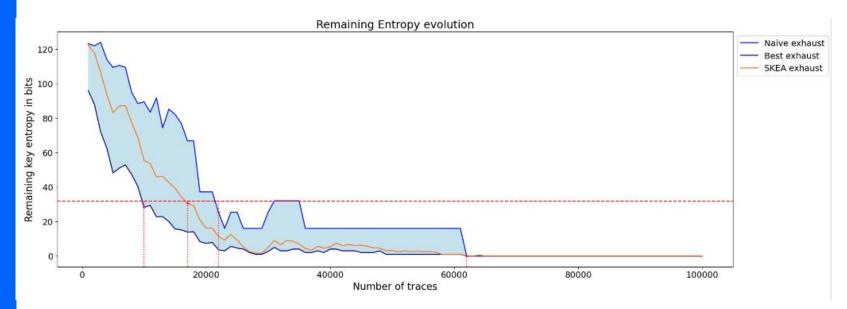

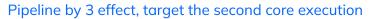

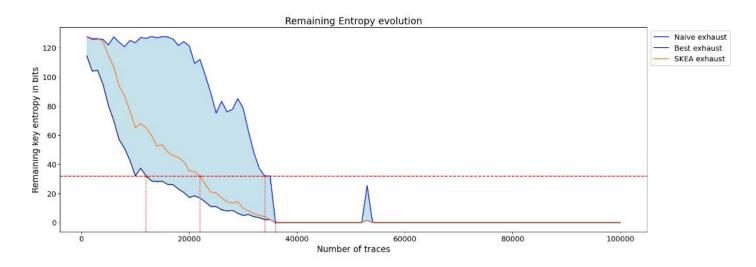

#### Pipeline by 3 effect target the first core execution

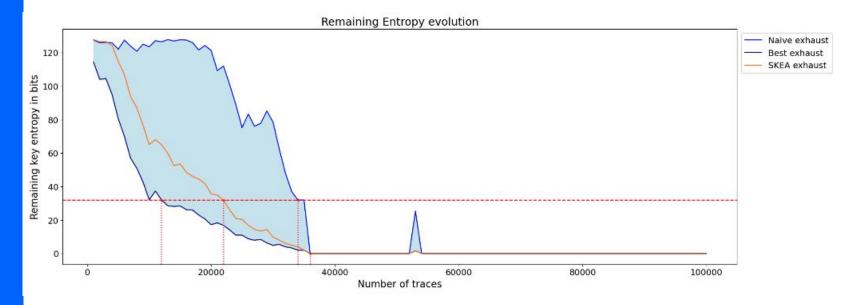

#### Pipeline by 3 effect, target the third core execution

With the proper Selection Function the third AES can be more easy to break

### Result

- → OS: Capture between interruptions

- → Cache: use cache activity as a helper, or remove bad traces

- → Pipeline : Leverage architecture and code knowledge to define the proper Selection Function

- → Litterature says 4 Million trace to attack an A53 we render with less than 40k or 20k to get 32-bit remaining entropy and get the whole key with SKEA

## **Faults?**

$\langle q \rangle$

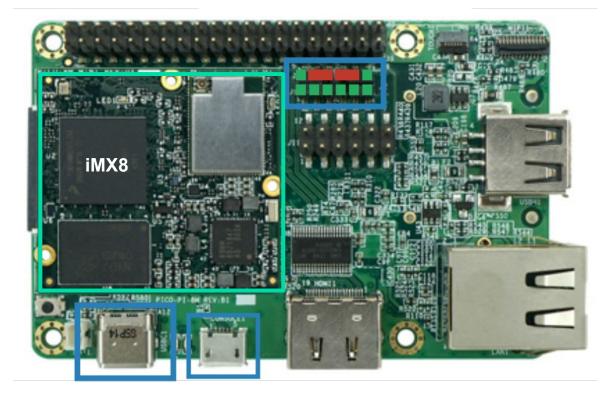

### Another SoC to play with : iMX8 mini

### Product description iMX8 mini

- → Motherboard Technexion PICO-PI-8M PICO-IMX8M-

- → Technology 14nm LPC FinFET

- → SoC: NXP **4x Cortex-A53** core platforms up to 1.8GHz per core

- → Caches

- 32kB L1-I Cache/ 32 kB L1-D Cache

- 512kB L2 Cache

### Methodology

- → Software stack analysis from OS to crypto routine call, understand how to reduce architecture effect.

- → Dedicated software (bare-metal) for characterization.

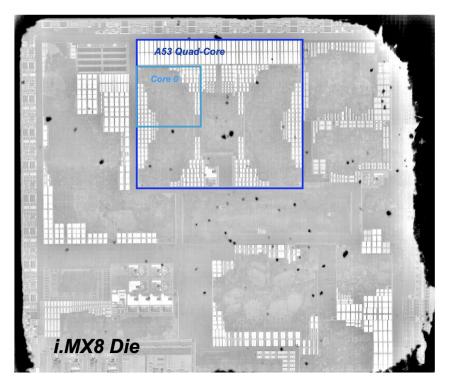

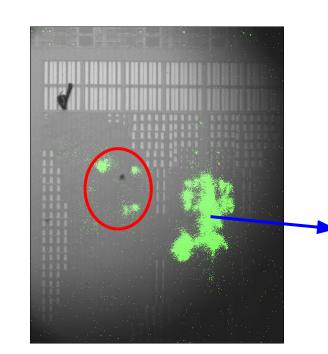

- → PhotoEmission to find area of activity and refine area of interest.

- → Simulation vs IRL comparison to explain or anticipate fault and leakage model.

- → Side-Channel Signal analysis to adjust timing and refine trigger, shooting delay ...

### Area Of Interest from EM-SCA

Area of interest

### **Area of Interest from Photonic Emission**

**Principle** Capture lots of images and stack them up to get highlighted activity by image processing.

**Not interesting** Area of cores Interconnect, (buses, I/O,...)

### Material for Laser Fault Injection

### Example of Fault Injection Parameter set

| EMFI Parameter  |                   | Range |      | Step (Coarse) | Step (Fine) | Unit |

|-----------------|-------------------|-------|------|---------------|-------------|------|

| X pos           | $\Leftrightarrow$ | 1000  | 2400 | 50 or 100     | 10 or 25    | μm   |

| Y pos           | \$                | 2200  | 3400 | 50 or 100     | 10 or 25    | μm   |

| Pulse amplitude | 4                 | 300   | 700  | 50 or 100     | 10          | V    |

| Pulse width     | X                 | 5     | 20   | 5             | 1           | ns   |

| Pulse delay     | Ó                 | 300   | 500  | 10            | 1           | μs   |

| Repeat          | 2                 | -     | step | 1             | 5           | #    |

| LFI Parameter | Range |      | Step (Coarse) | Step (Fine) | Unit    |    |

|---------------|-------|------|---------------|-------------|---------|----|

| X pos         | ⇔     |      |               | 10 or 6     | 3, 2, 1 | μm |

| Y pos         | \$    |      |               | н           | н       | μm |

| Optispot      | ۲     | 0    | 1500          | 100         | 10      | μm |

| PDM amplitude | 4     | 20   | 80            | 20          | 10      | %  |

| Pulse width   | X     | 100  | 1000          | 200         | 1       | ns |

| Pulse delay   | Ŏ     | 6875 | 8875          | 100         | -       | ps |

| Repeat        | ¢     | 0    | step          | 1           | 5       | #  |

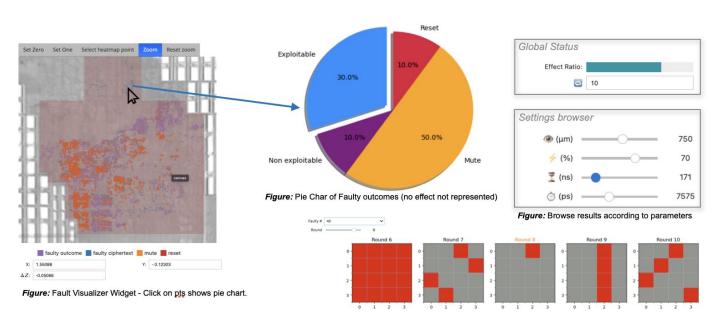

### **Fault Injection Exploitation**

Figure: Fault effect, back tracking knowing the key

## Thank you. Any questions?

- 🖂 contact@eshard.com

- www.eshard.com

- in /company/eshard

- 🥑 @eshard

#### France HQ

Bâtiment GIENAH 11 avenue de Canteranne 33600 Pessac, France

#### France R&D

7 rue Gaston de Flotte 13012 Marseille, France

#### Germany

eShard GmbH Beethovenallee 21 53173 Bonn