# On the way to secure random number generation

Patrick Haddad STMicroelectronics - Advanced System Technology

Viktor Fischer & Florent Bernard Université de Saint-Etienne- Laboratoire Hubert Curien

## Random numbers in cryptography

#### Usage of random numbers in cryptography:

- Cryptographic keys

- Initialization vectors

- Nonces

- Padding values

- Counter-measures against side-channel attacks

# Random number sequences are generated using random number generators:

- Pseudo-random number generators

- True random number generators

#### **Basic requirements on random sequences:**

- Good statistical quality

- Unpredictability and non-manipulability

Secure random number generators (RNG) in IC 1<sup>st</sup> security condition - unpredictability

#### **RNG used in ICs exploits noisy physical phenomenon**

Their exact name is : Physical True Random Number Generator (PTRNG) Secure PTRNG against non-invasive attacks 2<sup>nd</sup> security condition - non-manipulability

4

Recent works highlighted the random number unpredictability reduction with non-invasive attacks <sup>[1-4]</sup>

The unpredictability of the generated sequence is guaranteed

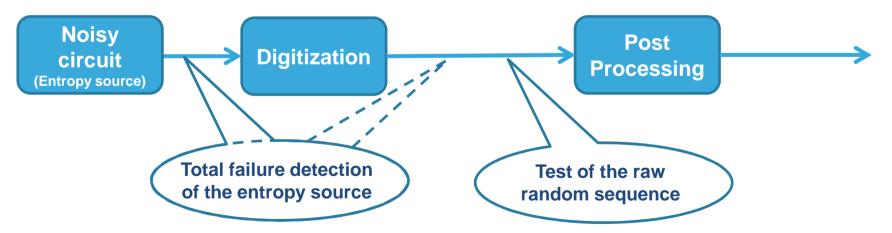

Check the quality of the generated sequence while the PTRNG is in operation (online tests)

AIS online tests recommendations (PTG2):

life.augmented

- [1]: K. Wold & al, Robustness of TRNG against Attacks that Employ Superimposing Signal on FPGA Supply Voltage (2010).

[2]: A. Markettos, The frequency injection attack on ring-oscillator-based true random number generators (2009).

- [3] : M. Soucarros & al , Influence of the temperature on true random number generators (2011).

[4]: P. Bayon & al, Contactless electromagnetic active attack on ring oscillator based true random number generator. (2012)

Overview of the presentation

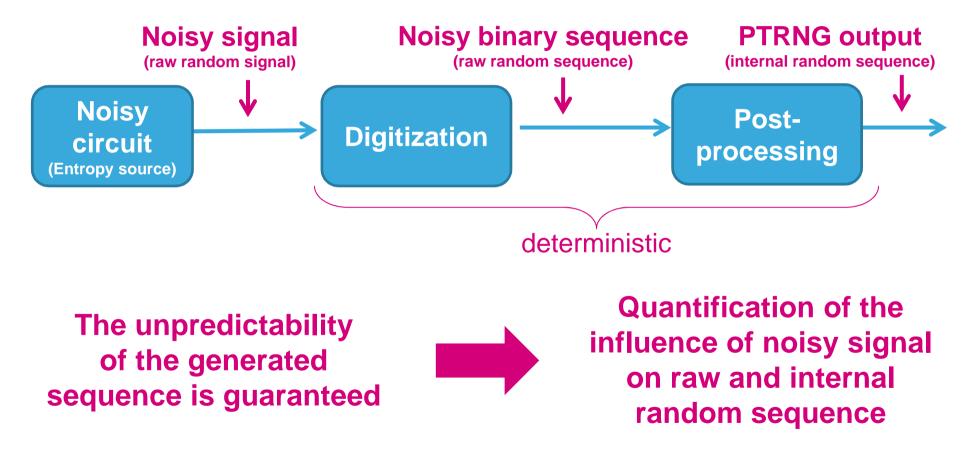

PTRNG secure Quantification of the influence of noisy signal on random sequences

Quality check of the generated sequence while the PTRNG is in operation (online tests)

We will present:

- A simple methodology to :

- Quantify the influence of noisy transistors on raw random sequence

- Help in the design of online tests

- Apply the proposed methodology to a PLL based PTRNG

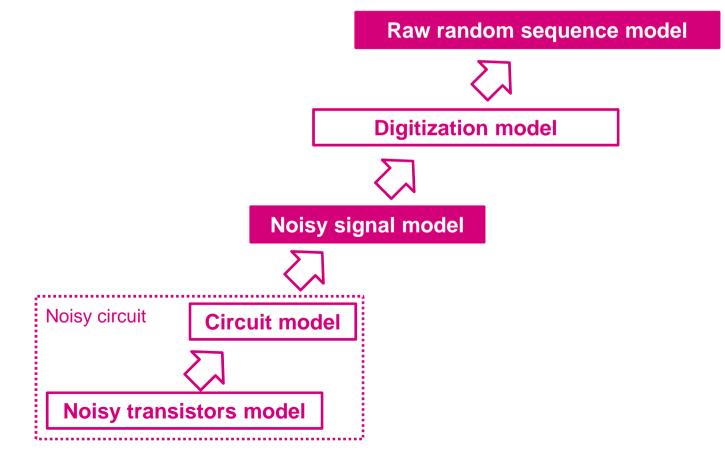

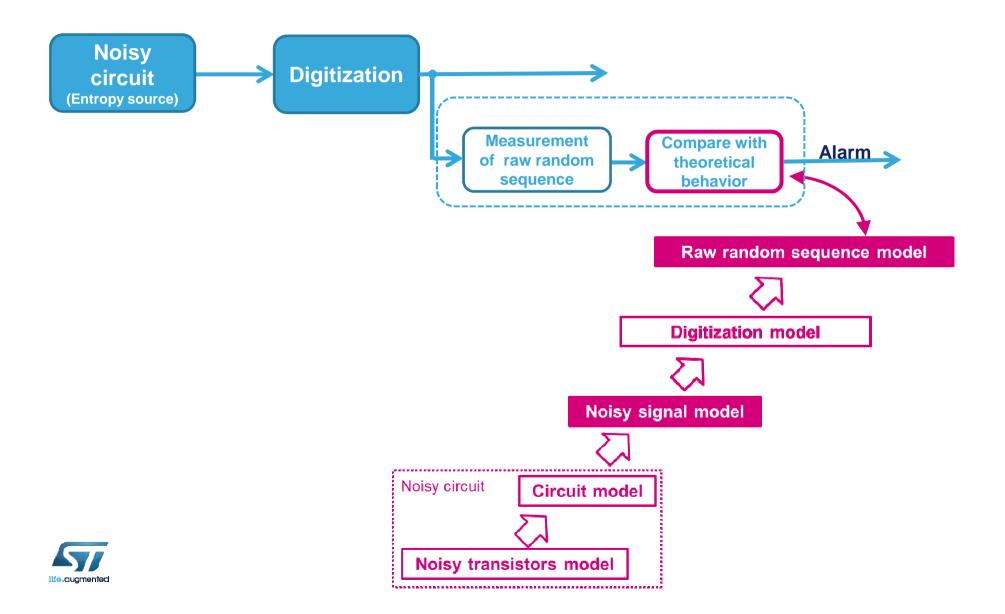

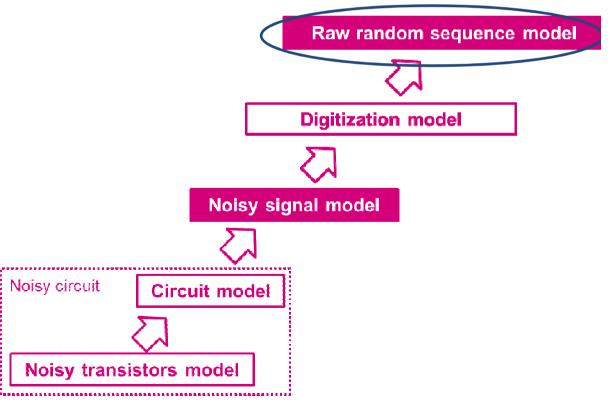

Methodology – a chain of models

# Objective: Quantify the impact of noisy transistors on generated raw random sequence

6

## Chain of models & online test

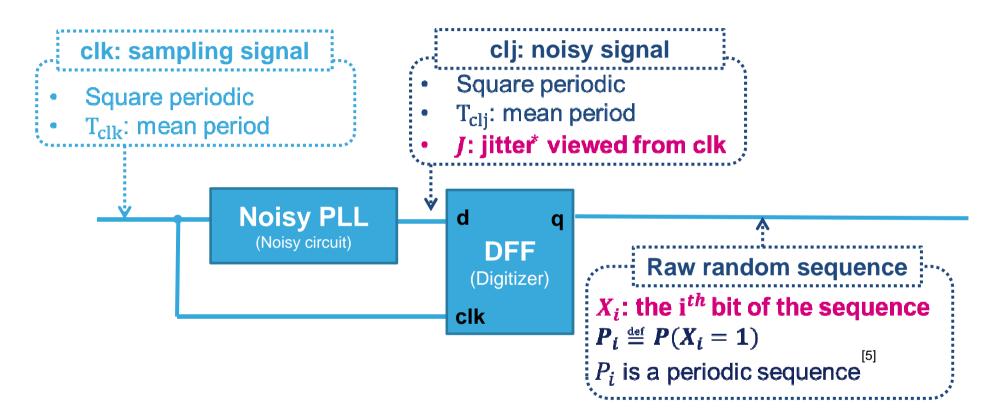

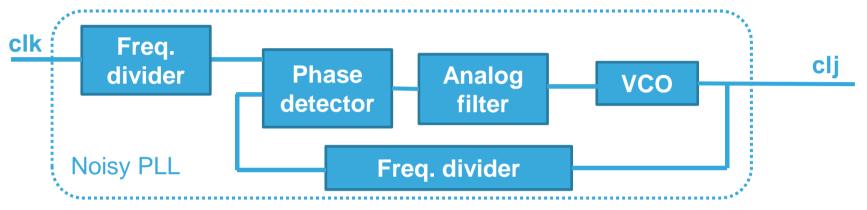

# Application of the proposed methodology to a PLL based PTRNG

## Application to the PLL based PTRNG

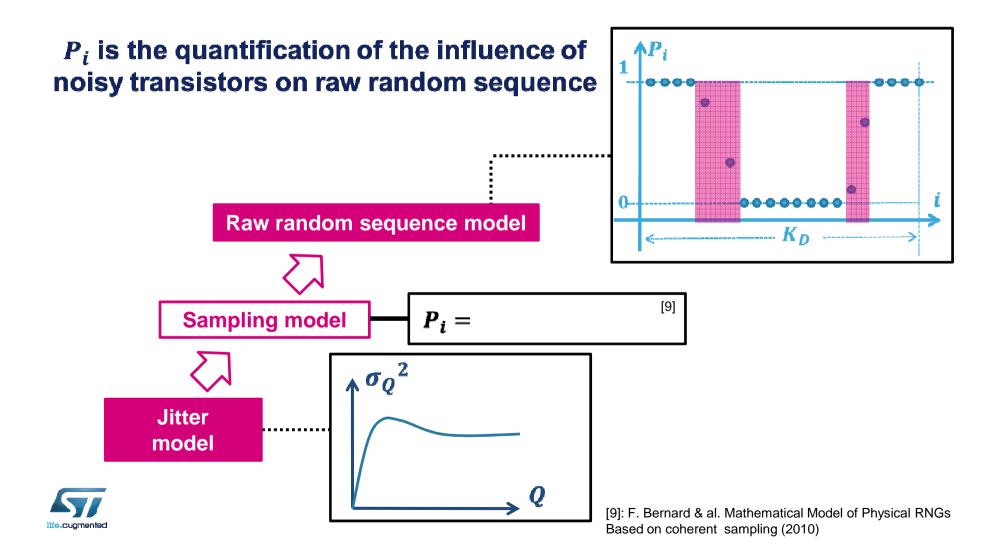

#### Next step : Establish theoretical values of P<sub>i</sub>

- Quantify the influence of noisy transistors on raw random sequence

- Use it as reference for online test

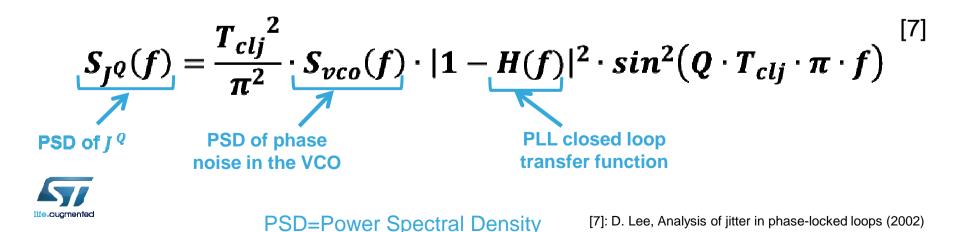

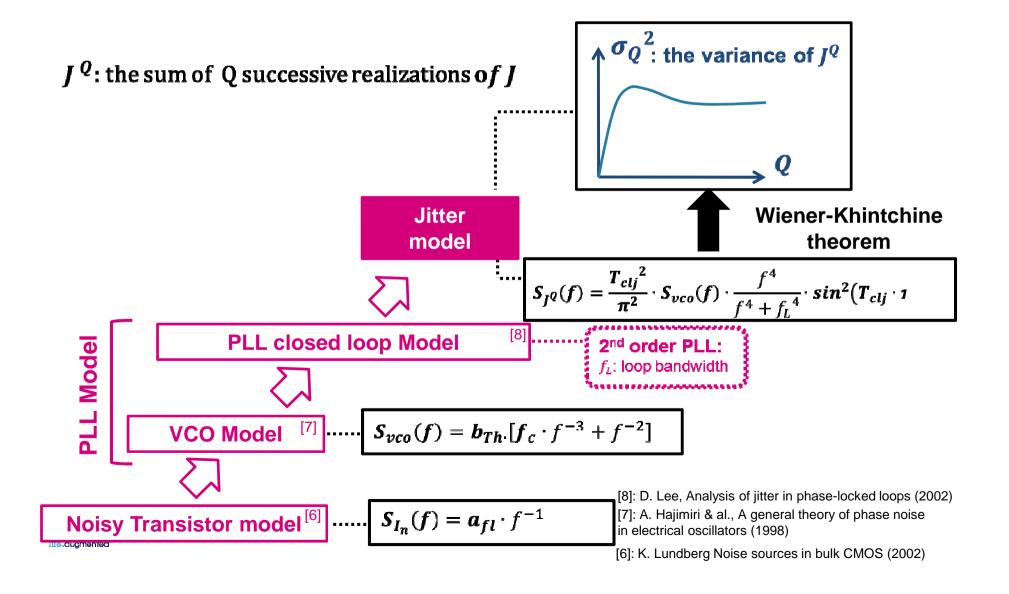

#### Chain of models for PLL base PTRNG Low level models

## Chain of models for PLL base PTRNG

Top level models

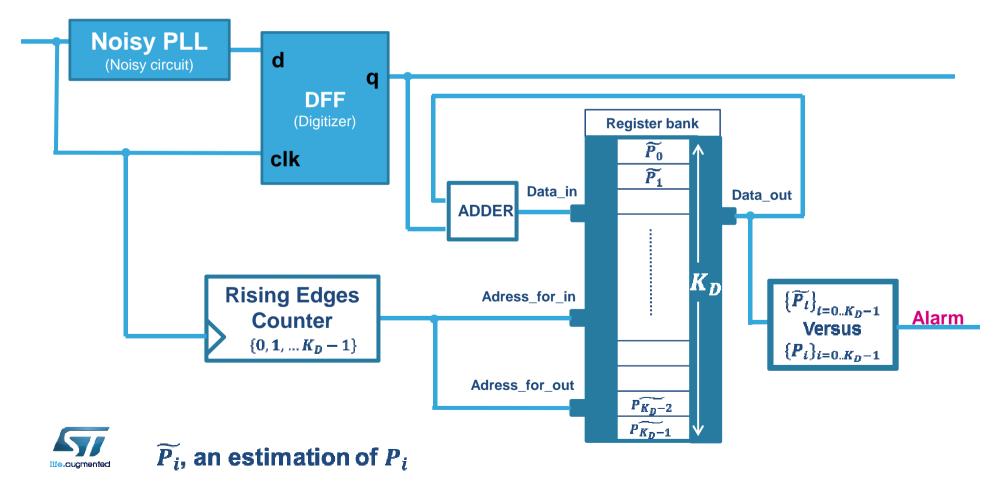

## Test of the raw random sequence

12

For testing the raw random sequence, we estimate a period of *P<sub>i</sub>* and compare it with theoretical values

## Summary

### We proposed :

## A chain of models : from transistor level to raw random bit level

- Quantify the influence of noisy transistors on raw random sequence

- Use a link as reference for online testing

## Summary

### We proposed :

## A chain of models : from transistor level to raw random bit level

- Quantify the influence of noisy transistors on raw random sequence

- Use a link as reference for online testing

#### We presented:

- The chain of models for the PLL based PTRNG

- PLL based PTRNG online test using on this chain of models

### We plan:

- Establish the chain of models for other PTRNG structures

- Design theirs online test using theses chains of models

# **Thank You**

15

#### A phase locked loop is an oscillator phase control system.

J<sup>Q</sup>: the sum of Q successive realizations of J